# From a FSM to a Digital Circuit & & Designing an Adder/Subtractor

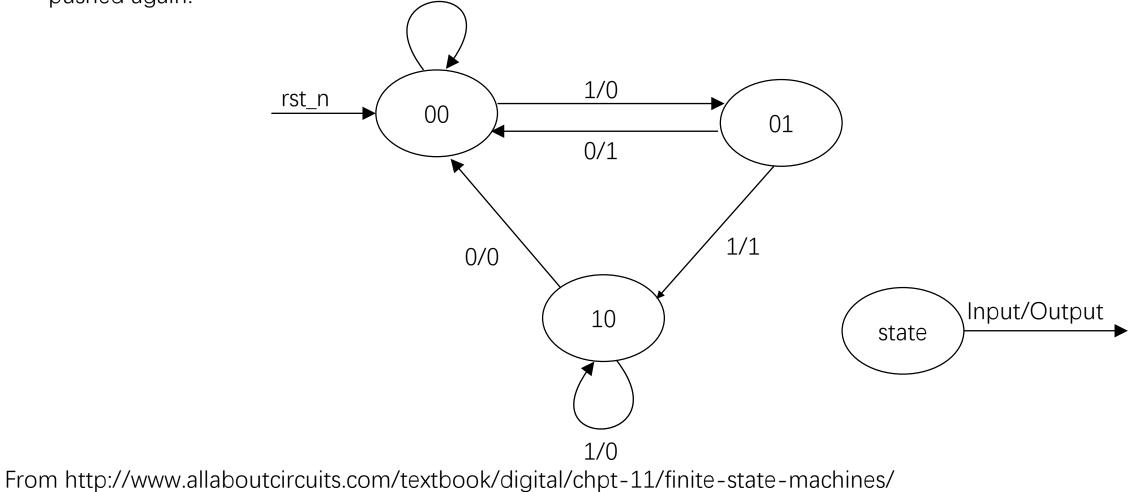

# The FSM Diagram

Function: Generate a positive pulse after the button is pushed. Keep 0 until the button is released and pushed again.  $\frac{0}{0}$

# From FSM to Truth Table

- List the input, current state, next state and output

- Empty states represented by X, will be useful later

| Current State         |                | Input Next State |        | State                   | Output |

|-----------------------|----------------|------------------|--------|-------------------------|--------|

| <i>S</i> <sub>1</sub> | S <sub>0</sub> | Ι                | $S'_1$ | <i>S</i> <sub>0</sub> ' | Y      |

| 0                     | 0              | 0                | 0      | 0                       | 0      |

| 0                     | 0              | 1                | 0      | 1                       | 0      |

| 0                     | 1              | 0                | 0      | 0                       | 1      |

| 0                     | 1              | 1                | 1      | 0                       | 1      |

| 1                     | 0              | 0                | 0      | 0                       | 0      |

| 1                     | 0              | 1                | 1      | 0                       | 0      |

| 1                     | 1              | 0                | Х      | Х                       | Х      |

| 1                     | 1              | 1                | Х      | Х                       | Х      |

#### Represent the states

- Represent a state by the output of several flip-flops

- Store the state value

- Can be changed at the rising edge of the clock

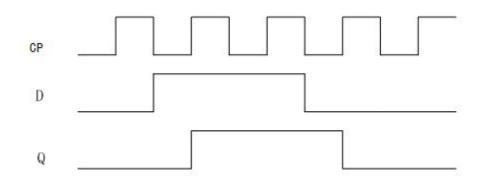

- A D-Flip Flop

- Output = Input at rising edge

- $ar{Q}$  is the complement of Q

- Set S=R=0 to use it as expected

- If S=R=1, output will always be 0

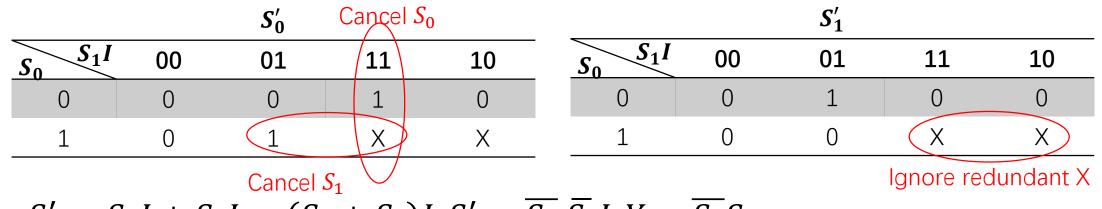

# Simplifying the logical representations

#### • Simplify the circuit with a Karnaugh Map

- Useful for 3 to 4 input variables (e.g., your next experiment)

- Hamming Distance of neighbor columns/rows = 1 (e.g., 01 and 11)

- Group 1's and X's together (1x2, 2x1, 2x2, 1x4, 4x1, etc.) and simplify

- $S_0S_1$  are inputs of the 2 D-Flip flops,  $S_0'S_1'$  are the outputs

•  $S'_0 = S_0 I + S_1 I = (S_0 + S_1) I, S'_1 = \overline{S_0} \, \overline{S_1} I, Y = \overline{S_0} S_1$

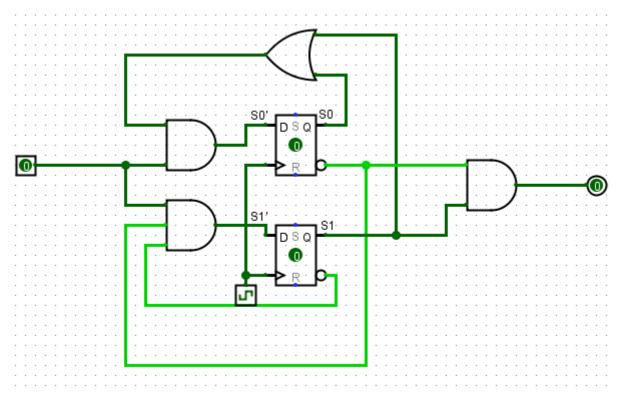

### Connect the circuit

•

$$S'_0 = S_0 I + S_1 I = (S_0 + S_1) I, S'_1 = \overline{S_0} \, \overline{S_1} I, Y = \overline{S_0} S_1$$

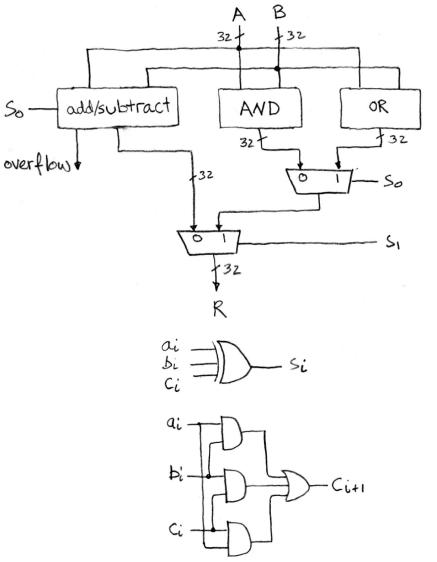

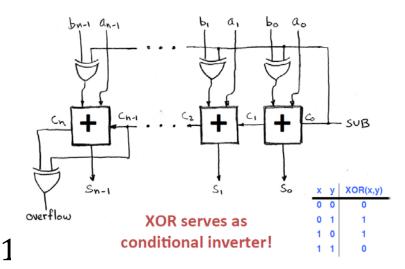

# Designing an Adder/Subtractor

- An adder/subtractor is a circuit that is:

- An adder when  $S_0 = 0$

- An subtractor when  $S_0 = 1$

- Required in ALU (top figure)

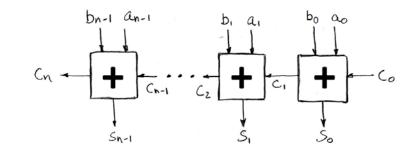

- Can be a cascade of 1-bit adders

- 1-bit adders(bottom figure):

- Input: *a*, *b*, *c*<sub>0</sub> (carry of last adder)

- Output: *s*, *c*<sub>1</sub> (sum and carry)

- Design by truth table.  $s = a \operatorname{xor} b \operatorname{xor} c$

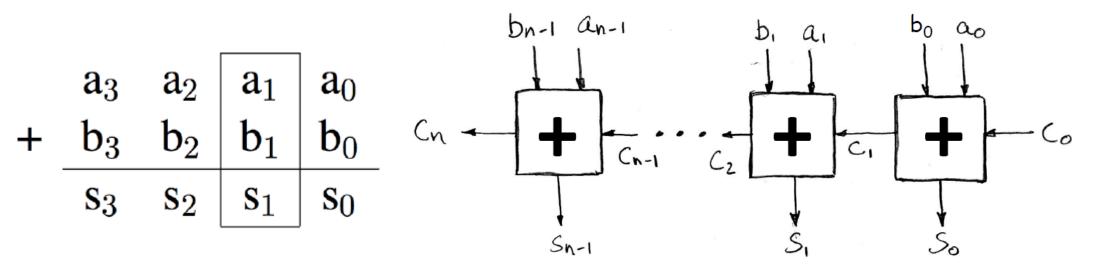

### Cascade of 1-bit adders into an adder

- Rather intuitive

- $C_n$  to represent overflow

#### Cascade of 1-bit adders into a subtractor

• How come?

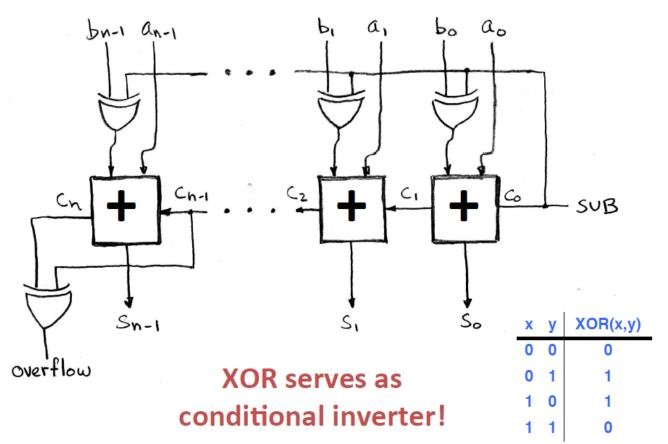

### Cascade of 1-bit adders into a subtractor

- *A*, *B* are n-bit numbers with signs

- $\tilde{A}$  is the 2's complement,  $\bar{A}$  is 1's complement

- Setting SUB = 1 to get  $\overline{B}$

- $b_i \operatorname{xor} SUB = b_i$  when SUB = 0

- $b_i \operatorname{xor} SUB = \overline{b_i}$  when SUB = 1

- Subtract to addition:  $A B = A + \tilde{B}$

- $-B = \tilde{B}$  considering only the lowest (n-1) bits:  $(-B)_{n-1} = (2^{n-1} + (-B))_{n-1} = (2^{n-1} - 1 - B) + 1$

Where  $(\cdot)_{n-1}$  represents taking the lowest (n-1) bits

# Overflow of n-bit adder

- Let A, B be the equivalent inputs to an n-bit adder

- If A > 0, B > 0

•

$$a_{n-1} = b_{n-1} = 0 \Rightarrow c_n = 0$$

- If overflow,  $c_{n-1} = 1$

- If *AB* < 0

- Overflow won't happen since  $|A + B| \leq |A|$

## Overflow of n-bit adder

- If A < 0, B < 0, we actually add their complements  $\overline{A}, \overline{B}$

- $a_{n-1} = b_{n-1} = 1 \Rightarrow c_n = 1$

- If overflow,  $c_{n-1} = 0$  (a bit tricky here)

- If  $(A + B)_{n-1} = 2^{n-1}$ , then  $A + B = -2^n$ , represented by  $0b100 \dots 0$ , not overflow

- Overflows when  $(A + B)_{n-1} > 2^{n-1}$  $\Rightarrow 2^{n-1} - \tilde{A}_{n-1} + 2^{n-1} - \tilde{B}_{n-1} > 2^{n-1} \Rightarrow \tilde{A}_{n-1} + \tilde{B}_{n-1} < 2^{n-1} \Rightarrow c_{n-1} = 0$

- To sum up, the addition overflows if and only if  $c_n \operatorname{xor} c_{n-1}$ =true

### The End