Datapath and TIPs for Processor Design

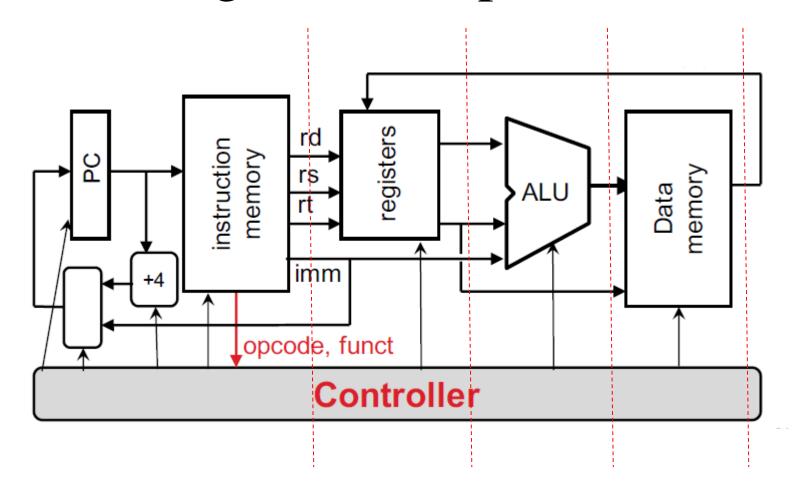

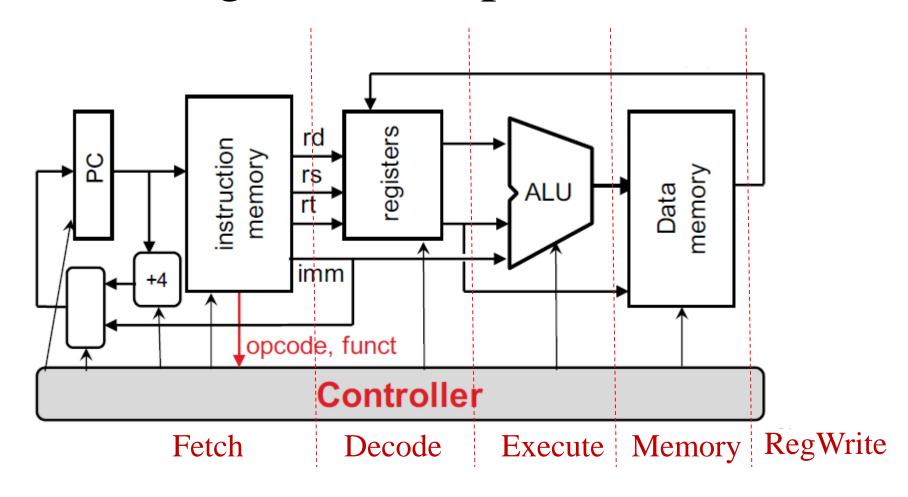

## Recall five stages on datapath

### Recall five stages on datapath

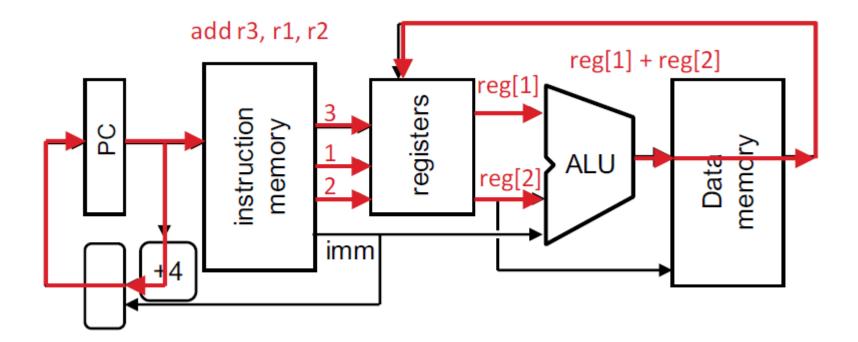

#### Recall Datapath Walkthroughs

• Take Add as an example

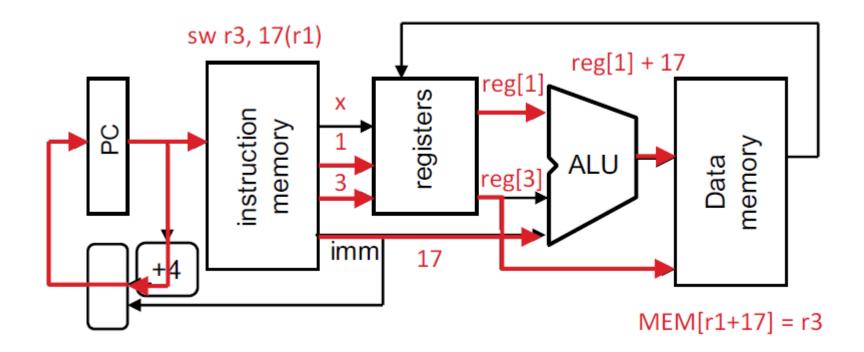

### Recall Datapath Walkthroughs

• Take sw as an example

# Single CPU Design

• Step1. Control signals for each operation

|     | Jump | Branch | RegDst | ExtOp | ALUSrc | MemWr | MemtoReg | RegWr |

|-----|------|--------|--------|-------|--------|-------|----------|-------|

| add |      |        |        |       |        |       |          |       |

| ori |      |        |        |       |        |       |          |       |

| lw  |      |        |        |       |        |       |          |       |

| beq |      |        |        |       |        |       |          |       |

| j   |      |        |        |       |        |       |          |       |

# Single CPU Design

• Step1. Control signals for each operation

|     | Jump | Branch | RegDst | ExtOp | ALUSrc | MemWr | MemtoReg | RegWr |

|-----|------|--------|--------|-------|--------|-------|----------|-------|

| add | 0    | 0      | 1      | X     | 0      | 0     | 0        | 1     |

| ori | 0    | 0      | 0      | 0     | 1      | 0     | 0        | 1     |

| lw  | 0    | 0      | 0      | 1     | 1      | 0     | 1        | 1     |

| SW  | 0    | 0      | X      | 1     | 1      | 1     | X        | 0     |

| beq | 0    | 1      | X      | 1     | 0      | 0     | X        | 0     |

| j   | 1    | X      | X      | X     | Х      | 0     | Х        | 0     |

## Single CPU to Two-Cycle CPU

## How can we deal with it?

Any questions about Project 2?