# Discussion: RISC-V Intro

SONGZE@SHANGHAITECH.EDU.CN

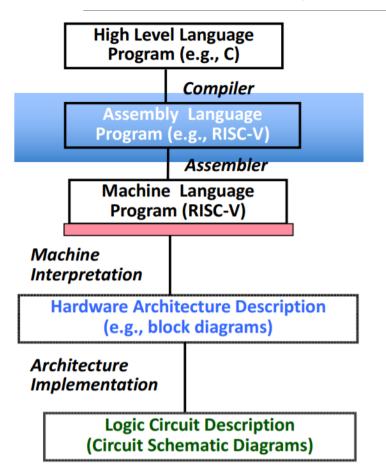

## Assembly language: RISC-V

Five

RISC-V: the 5<sup>th</sup> generation of RISC ISA

ISA: Instruction Set Architecture

RISC: Reduced Instruction Set Computing, e.g. MIPS, RISC-V

CISC: Complex Instruction Set Computing, e.g. x86

### Instructions

- Instruction is an atomic operation that a computer can do

- Most of them follow the format: A B, C, D

- But there are also exceptions will be covered later

- Instructions may deal with: registers; memory; immediate numbers.

- For a list of instructions, please refer to <u>Green card</u>.

### Registers

- RISC-V has 32 available registers.

- Extensions to RISC-V may enlarge that.

- Each register has 32-bit length .

- Our textbook uses 64-bit registers along with 64-bit memory address.

- Each register has a number(e.g. x10) and a name(e.g. a1).

- Details of names will be covered later.

- You should use a register's name rather than its number when programming.

- Registers have no type.

### Registers

- Important: registers are not variables and should NOT be used as variables!

- Registers are very limited in amount

- Recall the Great Idea #3: Principle of Locality/ Memory Hierarchy

- Store data in memory

- Load data from memory before use and save data back to memory after use

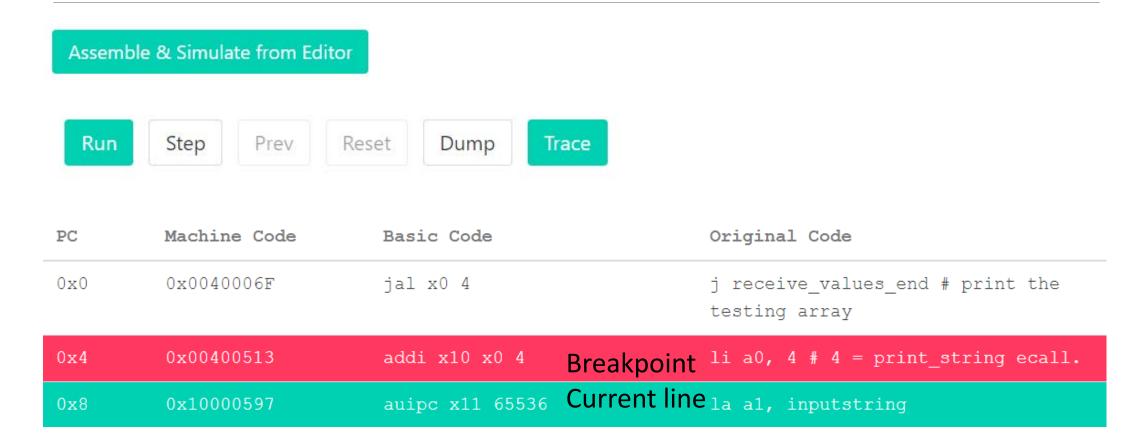

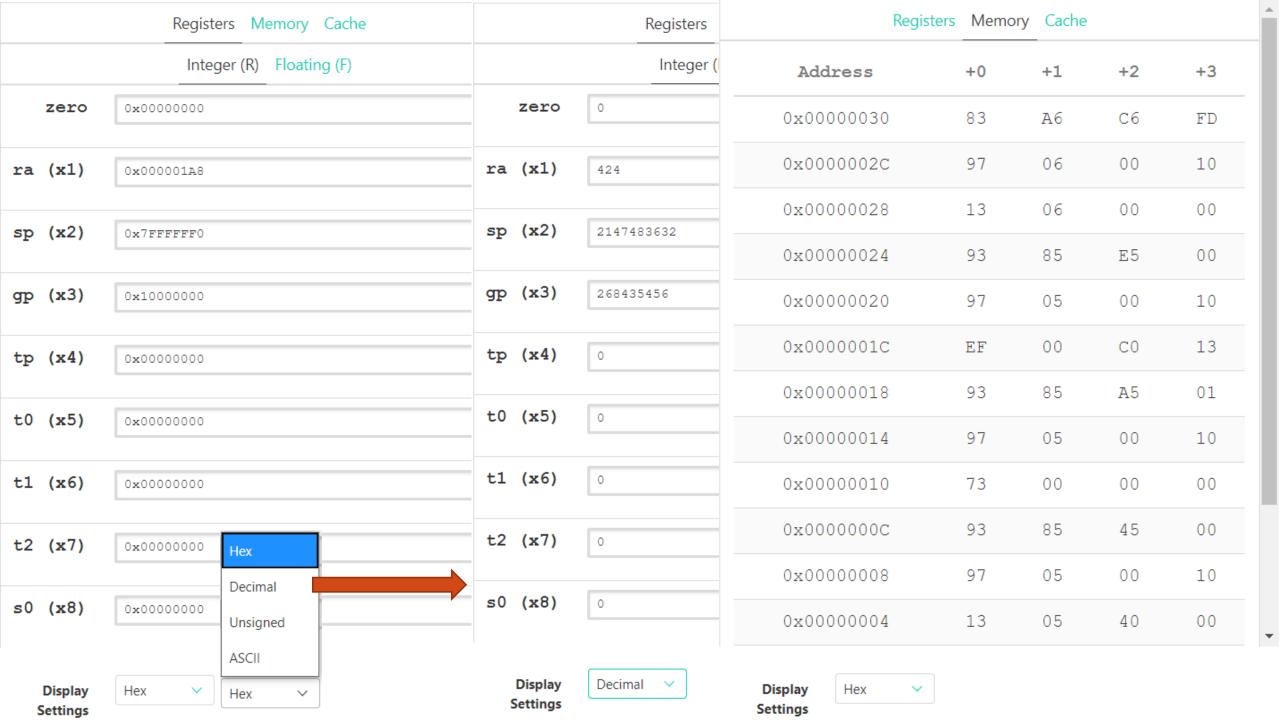

### Venus: A RISC-V simulator

- Webpage: <a href="http://autolab.sist.shanghaitech.edu.cn/venus/">http://autolab.sist.shanghaitech.edu.cn/venus/</a>

- With its GUI and tools, you can debug your assembly program very easily.

- Supports single step, previous step, breakpoints.

- You can see memory and register status real time.

|     |      |      |       |      |       | Address    | +0 | +1 | +2 | +3 |

|-----|------|------|-------|------|-------|------------|----|----|----|----|

| Run | Step | Prev | Reset | Dump | Trace | 0x00000018 | 33 | 03 | 63 | 02 |

|     |      |      |       |      |       | 0x00000014 | В3 | 03 | 63 | 00 |

#### How to use Venus

### Assembler directives

| Directive | Effect                                                                           |

|-----------|----------------------------------------------------------------------------------|

| .data     | Store subsequent items in the static segment at the next available address.      |

| .text     | Store subsequent instructions in the text segment at the next available address. |

| .byte     | Store listed values as 8-bit bytes.                                              |

| .asciiz   | Store subsequent string in the data segment and add null-terminator.             |

| .word     | Store listed values as unaligned 32-bit words.                                   |

### Access memory in RISC-V

- Use load/store instructions to access memory.

- Details will be covered in later lectures & discussions.

- Convention:

lw t0, sth

=======>

. data

sth: .word 0x1234ABCD

t0 (x5)

0x1234ABCD

Little Endian

| Address    | +0 | +1 | +2 | +3 |

|------------|----|----|----|----|

| 0x10000000 | CD | AB | 34 | 12 |

- RISC-V do not require mandatory memory alignment

- But you'd better follow this convention

| 1 | . data |       |            |

|---|--------|-------|------------|

| 2 | a:     | .word | 0x1234ABCD |

| 3 | b:     | .byte | 0xFF       |

| 4 | с:     | .word | 0xABCD1234 |

| 0x10000008 | AB | 00 | 00 | 00 |

|------------|----|----|----|----|

| 0x10000004 | FF | 34 | 12 | CD |

| 0x10000000 | CD | AB | 34 | 12 |

# Suggestions on programming in RISC-V

- Write some pseudo code / C code first, then translate into assembly.

- Write comments for every line or you will forgot what you have done very easily!

- Comment can be the C code / pseudo code that you refer to.

Use register names rather than numbers! (will be covered more later)