# Computer Architecture I Mid-Term

Chinese Name:

Pinyin Name:

Student ID:

E-Mail ... @shanghaitech.edu.cn:

| Question | Points | Score |

|----------|--------|-------|

| 1        | 1      |       |

| 2        | 3      |       |

| 3        | 10     |       |

| 4        | 7      |       |

| 5        | 6      |       |

| 6        | 8      |       |

| 7        | 4      |       |

| 8        | 2      |       |

| 9        | 9      |       |

| 10       | 13     |       |

| 11       | 21     |       |

| 12       | 16     |       |

| Total:   | 100    |       |

- This test contains 14 numbered pages, including the cover page, printed on both sides of the sheet.

- We will use gradescope for grading, so only answers filled in at the obvious places will be used.

- Use the provided blank paper for calculations and then copy your answer here.

- Please turn **off** all cell phones, smartwatches, and other mobile devices. Remove all hats and headphones. Put everything in your backpack. Place your backpacks, laptops and jackets out of reach.

- Unless told otherwise always assume a 32bit machine.

- The total estimated time is 120 minutes.

- You have 120 minutes to complete this exam. The exam is closed book; no computers, phones, or calculators are allowed. You may use two A4 pages (front and back) of handwritten notes in addition to the provided green sheet.

- There may be partial credit for incomplete answers; write as much of the solution as you can. We will deduct points if your solution is far more complicated than necessary. When we provide a blank, please fit your answer within the space provided.

- Do NOT start reading the questions/ open the exam until we tell you so!

1 1. First Task (worth one point): Fill in you name

Fill in your name and email on the front page and your ShanghaiTech email on top of every page (without @shanghaitech.edu.cn) (so write your email in total 14 times).

4

6

## 2. Various Questions

(a) Name the 6 Great Ideas in Computer Architecture as taught in the lectures.

# 3. C Basics

For this part, numbers are represented in 2's complement and stored in little endian. Except for decimals, please keep the leading zeros for full representation of the specified data length. All answers should adhere to the required format indicated by the subscripts.

(a) Consider the following numbers are stored in a signed short, figure out the arithmetic operations and fill the blanks.

$$(-813)_{10} >> (3)_{10} = (\underline{\qquad})_{16} \quad (02D7)_{16} + (00D6)_{16} = (\underline{\qquad})_{2}$$

$$(-1)_{10} \& (-2)_{10} = (\underline{\qquad})_{10} \qquad (FD94)_{16} - (727)_{10} = (\underline{\qquad})_{16}$$

(b) Read the declaration of the following union in C.

```

typedef union{

1

uint32_t number;

2

uint8_t bytes[4];

3

struct {

4

unsigned int x : 7;

5

unsigned int y : 5;

6

unsigned int z : 20;

7

} data;

8

9 } DataType;

```

- 1. What is the value of sizeof (DataType)?\_\_\_\_\_

- 2. Consider the assignment below, fill the following blanks.

```

DataType v;

v.number = 0x08C13D72;

```

```

v.data.x = (\__)_{16} v.data.y = (\__)_{16} v.data.z = (\__)_{16}

3. Consider another assignment below, fill the following blanks.

```

```

1 DataType v;

2 v.data.x = 0x7A;

3 v.data.y = 0x03;

4 v.data.z = 0xCEF3D;

v.bytes[0] = (_____)_{16} v.bytes[1] = (_____)_{16}

v.bytes[2] = (_____)_{16} v.bytes[3] = (_____)_{16}

```

3

# 4. Memory in C

Consider the following C program, fill in the blanks.

| 1   | <pre>#define MAX_NAME_LEN 50</pre>                        |                                                                                                  |

|-----|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| 2   | <pre>int num_people = 0;</pre>                            |                                                                                                  |

| 3   | <pre>void add_people(char **list) {</pre>                 |                                                                                                  |

| 4   | <pre>char name2[] = "Van";</pre>                          |                                                                                                  |

| 5   | list[num_people] = calloc(N                               | MAX_NAME_LEN, sizeof(char));                                                                     |

| 6   | <pre>strcpy(list[num_people], na</pre>                    | ame2);                                                                                           |

| 7   | num_people += 1;                                          |                                                                                                  |

| 8   | }                                                         |                                                                                                  |

| 9   | <pre>int main(){</pre>                                    |                                                                                                  |

| 10  | <pre>const int list_size = 100;</pre>                     |                                                                                                  |

| 11  | <pre>char **name_list = malloc(s</pre>                    | <pre>sizeof(char *) * list_size);</pre>                                                          |

| 12  | <pre>char *name1 = "Billy";</pre>                         |                                                                                                  |

| 13  | <pre>add_people(name_list);</pre>                         |                                                                                                  |

| 14  | <pre>add_people(name_list);</pre>                         |                                                                                                  |

| 15  | return 0;                                                 |                                                                                                  |

| 16  | }                                                         |                                                                                                  |

| (a) |                                                           | these four questions based on what the given C<br>ime malloc return heap address sequentially in |

|     | name_list                                                 | &list_size                                                                                       |

|     | &name_list                                                | #_people                                                                                         |

|     | name_list[1]                                              | name_list                                                                                        |

|     | &name1                                                    | &list                                                                                            |

| (b) | Fill in static, stack, heap or co address type in memory. | de for these three questions according to their                                                  |

name1 \_\_\_\_\_

| *name_list |  |

|------------|--|

|            |  |

&(name2[1])

|2|

4

4

4

#### 5. Superscalar

(a) Both VLIW and out-of-order superscalar processors exploit instruction-level parallelism. Which one adds more complexity to the hardware and which one adds more complexity to the compiler?

Hardware:

Compiler:

(b) Are the concepts of superscalar processing and out-of-order execution independent of each other? Why or why not? Explain and justify in no more than 20 words.

#### 6. Number Representation

(a) Consider this 8-bit binary pattern 0b11001010, please write down this number if we are using the following representations:

| Unsigned binary         | Sign-Magnitud | le binary |

|-------------------------|---------------|-----------|

| Two's complement binary | Hex           | adecimal  |

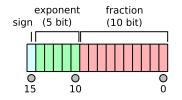

(b) Suppose we are using half-precision floating-point (16-bit) format (like on NVIDIA GeForce FX). The layout for the 16-bit floating point is:

Everything else follows the IEEE 754 standard for floating point, except bias. Answer the following questions.

What is the bias?

What is the smallest positive denorm?

Convert -10.8125 to 16-bit floating point. Write in hexadecimal.

Convert 0xCA20 into decimal.

# 7. SDS

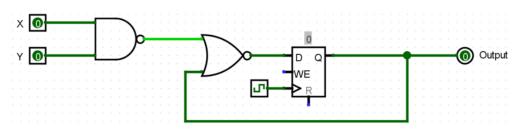

(a) Draw the Timing Diagram for the circuit below. The delay for the gates are 10 ns, the clock-to-q delay for a register is 20 ns, each clock cycle is 80 ns, each grid in the following diagram is a unit of 10 ns. The output is initially given in the graph.

Use any of those graphs to put in your answer (so you can re-do it). Clearly mark your final answer if you use more than one graph!

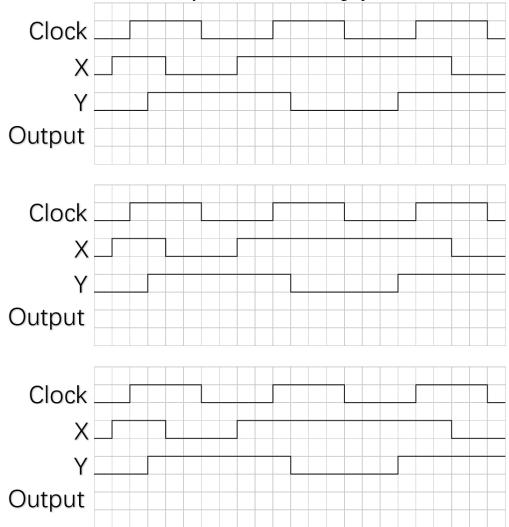

# 8. Circuit time calculation

In this circuit below, RegA and RegB have setup, hold and clk-to-q times of 8ns, NOT logic gate has a delay of 1ns, AND logic gate has a delay of 3ns, XNOR logic gate has a delay of 5ns, and RegC has a setup time of 9ns.

(a) What is the minimum acceptable clock cycle time for this circuit, and the clock frequency this corresponds to?

**Clock cycle time:**

**Clock frequency:**

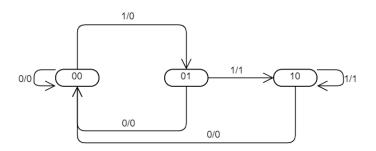

9. FSM and Truth Table

2

2

3

(a) Fill in the truth table for the FSM.

| state bit1 | state bit0 | input | next state bit1 | next state bit0 | output |

|------------|------------|-------|-----------------|-----------------|--------|

| 0          | 0          | 0     |                 |                 |        |

| 0          | 0          | 1     |                 |                 |        |

| 0          | 1          | 0     |                 |                 |        |

| 0          | 1          | 1     |                 |                 |        |

| 1          | 0          | 0     |                 |                 |        |

| 1          | 0          | 1     |                 |                 |        |

- (b) Using st1(state bit1), st0(state bit0) and ip(Input) as the input and Output as the output, extract a boolean expression from your table.

- (c) What does the given FSM implement (Describe when the FSM will output 1)?

- (d) Extend and modify the given FSM to make it output 1 if and only if the FSM receives input sequence including "110"Draw the diagram below:

# 10. RISC-V Programming

Look at the following RISC-V function that sorts an word array in-place, whose start address is given in a0 and length given in a1.

|   | 1   | sort:                                                                                                                                                    |

|---|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 2   | # prologue                                                                                                                                               |

|   | 3   | mv s0, a0                                                                                                                                                |

|   | 4   | 0x00259493                                                                                                                                               |

|   | 5   | addi s1, s1, -4                                                                                                                                          |

|   | 6   | add s1, s1, s0                                                                                                                                           |

|   | 7   | mv t0, s0                                                                                                                                                |

|   | 8   | outer_loop:                                                                                                                                              |

|   | 9   | mv t1, t0                                                                                                                                                |

|   | 10  | 0x00032383                                                                                                                                               |

|   | 11  | mv t3, t1                                                                                                                                                |

|   | 12  | inner_loop:                                                                                                                                              |

|   | 13  | addi t1, t1, 4                                                                                                                                           |

|   | 14  | lw t4, 0(t1)                                                                                                                                             |

|   | 15  | ble t4, t2, mystery_label                                                                                                                                |

|   | 16  | mv t2, t4                                                                                                                                                |

|   | 17  | mv t3, t1                                                                                                                                                |

|   | 18  | mystery_label:                                                                                                                                           |

|   | 19  | blt t1, s1, inner_loop                                                                                                                                   |

|   | 20  | lw t5, 0(t0)                                                                                                                                             |

|   | 21  | sw t2, 0(t0)                                                                                                                                             |

|   | 22  | sw t5, 0(t3)                                                                                                                                             |

|   | 23  | addi t0, t0, 4                                                                                                                                           |

|   | 24  | blt t0, s1, outer_loop                                                                                                                                   |

|   | 25  | # epilogue                                                                                                                                               |

|   | 26  | ret                                                                                                                                                      |

| 2 | (a) | Please disassemble machine code marked #p1 and #p2 above to RISC-V instructions. (Please use register names, e.g. s0, s1, etc., <b>NOT</b> x8, x9, etc.) |

|   |     | 0x00259493  # p1:                                                                                                                                        |

|   |     | 0x00032383  # p2:                                                                                                                                        |

| 2 | (b) | How many different types of pseudo instructions appeared above? (Instructions with different names are considered different types.) Please list them.    |

| 4 | (c) | "li x1, 0xDCBAABCD" is also a pseudo instruction. Below it's expanded to 2 normal                                                                        |

|   |     | instructions. Please fill in the blanks and translate each of them to machine code.                                                                      |

|   |     | lui x1, 0x: 0x                                                                                                                                           |

|   |     | addi x1,: 0x                                                                                                                                             |

Midterm, Page 9 of 14

memset () is a function defined in standard C library, it fills a byte string with a byte value and can be implemented as follows:

```

#include <stddef.h>

1

2

void *memset(void *dst, int c, size_t len) {

3

char *start = dst, *end = start + len;

4

for (char *ptr = dst; ptr < end; ++ptr) {</pre>

5

*ptr = (unsigned char) c;

6

}

7

return dst;

8

9 }

```

5

(d) Please implement memset () function in RISCV assembly. Your memset () function should fills the first len bytes of the memory area pointed to by dst with the constant byte c and returns its first argument.

| loop:  |      |      |

|--------|------|------|

|        |      |      |

| contir | ret  |      |

| CONTI  | iue: |      |

|        |      |      |

|        |      | 1    |

|        | J    | loop |

### 11. Cache

2

memset:

(a) The Average Memory Access Time equation (AMAT) has three components: hit time, miss time, and miss penalty. For each of the following cache optimizations, indicate which component of the L1 AMAT equation may be *improved*. Circle one.

| Using a second-level cache        | hit time | miss rate | miss penalty |

|-----------------------------------|----------|-----------|--------------|

| Using larger blocks               | hit time | miss rate | miss penalty |

| Using a smaller first-level cache | hit time | miss rate | miss penalty |

| Using a larger first-level cache  | hit time | miss rate | miss penalty |

- (b) Consider a 32-bit physical memory space and a 32 KiB 2-way set associative cache with LRU replacement. You are told the cache uses 5 bits for the offset field.

- 1. Write in the number of bits in the tag and index fields.

| TAG | Set index | Block offset |

|-----|-----------|--------------|

|     |           | 5 bits       |

2. Given the following C source code,

```

int ARRAY_SIZE = 64 * 1024;

int arr[ARRAY_SIZE]; // *arr is aligned to a cache block

/* loop 1 */

for (int i = 0; i < ARRAY_SIZE; i += 8) arr[i] = i;

/* loop 2 */

for (int i = ARRAY_SIZE - 8; i >= 0; i -= 8) arr[i+1] =

arr[i];

```

What is the hit rate of loop 1? What types of misses (of the 3 Cs), if any, occur as a result of loop 1?

What is the hit rate of loop 2? What types of misses (of the 3 Cs), if any, occur as a result of loop 2?

3

# (c) This section involves T / F questions. Circle the correct answer. Notice: NO selection will be treated as a wrong choice.

T / F: The local miss rate of one level of a cache is always greater than the global miss rate of that cache.

T / F: Any cache miss that occurs when the cache is full is a capacity miss.

T / F: The only way to remove capacity miss is to increase the cache capacity.

T / F: For the same cache size and block size, a 4-way set associative cache will have more index bits than a direct-mapped cache.

T/F: The hit rate of a combined cache is usually worse than the two split caches which have the same size in sum with the combined cache.

T/F: The index of a cache block, together with the tag contents of that block, uniquely specifies the memory address of the word contained in the cache block.

6

### (d) AMAT Calculation

Suppose your system consists of:

- An L1 cache that has a hit time of 5 cycles and has a local miss rate of 20%.

- An L2 cache that has a hit time of 20 cycles and has a local miss rate of 15%.

- An L3 cache that has a hit time of 200 cycles and has a local miss rate of 5%.

- Main memory hits in 1000 cycles.

**Notes:** You should show your calculation process. Only giving a solution will receive no point.

1. What is the global miss rate?

2. What is the AMAT of the system?

(e) Consider the following program and cache behaviors.

| Data Reads per    | Data Writes per   | Instruction Cache | Data Cache | Block Size |

|-------------------|-------------------|-------------------|------------|------------|

| 1000 Instructions | 1000 Instructions | Miss Rate         | Miss Rate  | (bytes)    |

| 250               | 150               | 0.30%             | 2%         | 64         |

Suppose a CPU with a write-through, write-allocate cache achieves a CPI of 2. What are the read and write bandwidths (measured by bytes per cycle) between RAM and the cache? (Assume each miss generates a request for one block.)

**Notes:** You should show your calculation process. Only giving a solution will receive no point.

|2|

2

2

## 12. **RISC-V** pipelining

(a) please circle the correct answer. Notice: NO selection will be treated as a wrong choice.

T / F: Pipelining the CPU datapath results in instructions being executed with higher latency and throughput

T / F: Without forwarding, data hazards will usually result in 3 stalls

T / F: All data hazards can be resolved with forwarding

T / F: Control hazards are caused byjump and branch instructions

The delays of circuit elements of a datapath are given as follows:

| Element   | Register       | Register    | MUX       | ALU       | Mem           | Mem            | RegFile      | RegFile       | branch      |

|-----------|----------------|-------------|-----------|-----------|---------------|----------------|--------------|---------------|-------------|

|           | clk-to-q       | Setup       |           |           | Read          | Write          | Read         | Setup         | comp        |

| Parameter | $t_{clk-to-q}$ | $t_{setup}$ | $t_{mux}$ | $t_{ALU}$ | $t_{MEMread}$ | $t_{MEMwrite}$ | $t_{RFread}$ | $t_{RFsetup}$ | $t_{Bcomp}$ |

| Delay(ps) | 30             | 20          | 25        | 200       | 150           | 125            | 130          | 20            | 75          |

Answer the following questions.

- (b) What was the clock time and frequency of a single cycle CPU?

- (c) What is the clock time and frequency of a pipelined CPU?

- (d) What is the speed-up? Why is it less than five?

Consider the following 3 datapaths:

|           | Stage1 | Stage2 | Stage3 | Stage4 | Stage5 | Stage6 |

|-----------|--------|--------|--------|--------|--------|--------|

| Datapath1 | IF     | ID     | EXE    | MEM    | WB     | -      |

| Datapath2 | IF     | ID     | EXE1   | EXE2   | MEM    | WB     |

| Datapath3 | IF/ID  | EXE1   | EXE2   | MEM    | WB     | -      |

The execution time of these datapaths are listed below:

|           | Stage1 | Stage2 | Stage3 | Stage4 | Stage5 | Stage6 |

|-----------|--------|--------|--------|--------|--------|--------|

| Datapath1 | 200ps  | 150ps  | 350ps  | 170ps  | 130ps  | -      |

| Datapath2 | 220ps  | 180ps  | 100ps  | 200ps  | 250ps  | 150ps  |

| Datapath3 | 400ps  | 200ps  | 200ps  | 250ps  | 150ps  | -      |

1

3

2

(e) Which datapath is the same as RISC-V datapath as learned in class?

(f) Without pipelining, what's the maximum clock rate of Datapath3?

- (g) What method can you use to improve performance?

- (h) With pipelining, what's the maximum clock rate of each datapath?

- (i) In this question, you'll only need to consider **Datapath1**. Which of the following instruction(s) exercise the critical path?

- A. add

- $B. \; \texttt{lw}$

- C. mul

No question here!