## Computer Architecture Homework 4

Spring 2019, March

## 1 Synchronous Finite State Digital Machine Systems

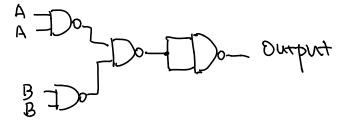

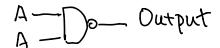

a. The circuit shown below can be simplified. Write a Boolean expression that represents the function of the simplified circuit using the minimum number of AND, OR, and NOT gate.

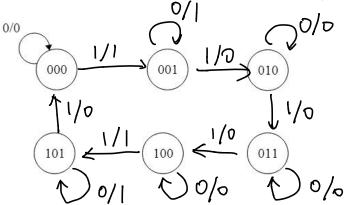

b. Consider the finite state machine below which has 6 states and a single input that can take on the value of 0 and 1. The finite state machine should output 1 IF AND ONLY IF 6 + sum of all the input values is not divisible by 2 or 3. One transition has been provided; complete the remainder of the diagram. (Hint: If the sum of the inputs is a multiple of 6, then we have 6 + sum of the inputs = 6 n for some n. As 6 n is divisible by 2, 6 n cannot be prime.)

c. Consider the following circuit. Assume registers have a CLK to Q time of  $60 \mathrm{ps}$ , a setup time of  $40 \mathrm{ps}$ , and a hold time of  $30 \mathrm{ps}$ . Assuming that all gates have the same propagation delay, what is the maximum propagation delay each individual gate could have to achieve a clock rate of 1 GHz.

CL = 300 PS.

Sol: 300 ps.

clock rate = |GHZ > maximum clock period = 1000 ps.

The critical path includes: 3 combinational logic,

1 CLK-to-Q, 1 set up time.

3 \* CL + 60 ps + 40 ps = 1000 ps.

## 2 Boolean Logic

1. Simplify each Boolean expression to one of the following ten expressions:  $0, 1, A, B, AB, A+B, \overline{A} \ \overline{B}, \overline{A} + \overline{B}, A\overline{B}, \overline{A}B$ Each answer may be used as many times as necessary.

$$a.A(A + \overline{A}) + B$$

b.

$$(A+B)(\overline{A}+B)\overline{B}$$

$\Rightarrow (AB+B\overline{A}+B)\overline{B}$

$\Rightarrow B \cdot \overline{B} \Rightarrow 0$

c. $\overline{A+B}$

$\Rightarrow \overline{A} \overline{B} \Rightarrow AB$

2. Simplify the following expression step by step (as simple as possible):

b. Grouping & Extra Terms:

$$\overline{A} \overline{B} \overline{C} + \overline{A}B\overline{C} + AB\overline{C} + A\overline{B} \overline{C} + ABC + A\overline{B}C$$

$$= \overline{A} \overline{C} (\overline{B} + B) + \overline{A} \overline{C} (\overline{B} + \overline{B}) + \overline{A} \overline{C} (\overline{B} + \overline{B})$$

$$= \overline{A} \overline{C} + \overline{A} \overline{C} + \overline{A} \overline{C}$$

$$= \overline{A} \overline{C} + \overline{A} \overline{C} + \overline{A} \overline{C} + \overline{A} \overline{C}$$

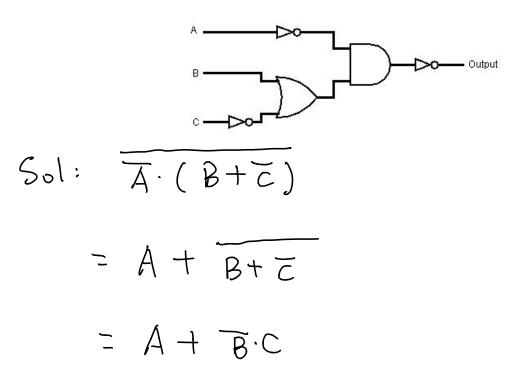

c. DeMorgan's:  $\overline{A(\overline{B} \overline{C} + BC)} = (\overline{A} + \overline{A}) \overline{C} + \overline{A} (\overline{C} + \overline{C})$

$$= \overline{A} + \overline{B} \overline{C} + \overline{B} \overline{C}$$

$$= \overline{C} + \overline{A}$$

$$= \overline{A} + \overline{B} \overline{C} \overline{B} \overline{C}$$

$$= \overline{A} + (\overline{B} + C)(\overline{B} + \overline{C})$$

$$= \overline{A} + \overline{B} \overline{C} + \overline{B} \overline{C}$$

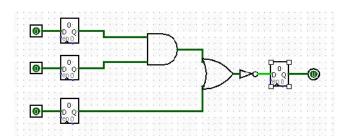

## 3 Logic Gates

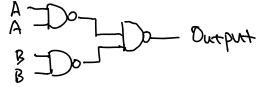

a. Create a NOT gate using only NAND gates.

b. Create an AND gate using only NAND gates. (Hint: use a)

c. Create an OR gate using only NAND gates.

d. Create a NOR gate using only NAND gates. (Hint: use a &~c)